- Vitis 统一软件平台

适合从边缘到云的所有开发者

Vitis™ 统一软件平台简介.

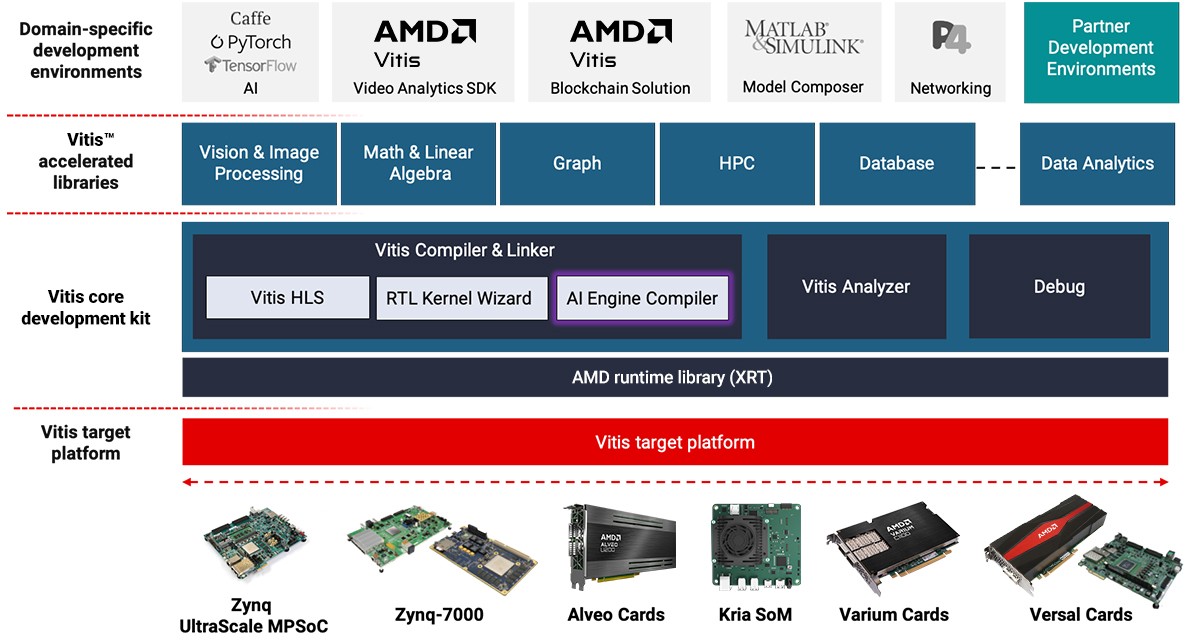

Vitis 统一软件平台包括:

- 全面的内核开发套件,可无缝构建加速应用

- 完整的硬件加速开源库,针对 AMD FPGA 和 Versal™ 自适应 SoC 硬件平台进行了优化

- 插入特定领域的开发环境,可直接在熟悉的更高层次框架中进行开发

- 不断发展的硬件加速合作伙伴库和预建应用生态系统

- Vitis Model Composer 是一款基于模型的设计工具,不仅可在 MathWorks MATLAB® 和 Simulink® 环境中实现快速设计探索与验证 ,而且还可加速 AMD 器件的生产进程。

- Vitis Networking P4 允许创建软定义网络。VitisNetP4 数据平面构建器生成的系统可以针对从简单的数据包分类到复杂的数据包编辑的各种数据包处理功能进行编程。

在 Vitis 环境中开发,无论您是从概念验证或开发套件移植,还是从定制开发板移植,均可实现平台与平台间的可移植性。 基于 Vitis 平台的设计方法提供了众多生产力优势。

- 平台重用:在同一平台上互换不同的加速应用。

- 应用可移植:跨不同平台轻松移植应用

- 仿真时间:使用内核加速协同仿真

- 运行时:开源运行时,通过 PCIe® 或嵌入式接口处理主机与器件之间的通信

- 系统调试:通过协同仿真完整系统保存完整的硬件编译

Vitis 统一软件平台的重要组件

Vitis AI 开发环境

Vitis AI 开发环境是一个专门的开发环境,用于在 AMD 嵌入式平台、Alveo 加速卡或云端 FPGA 实例上加速 AI 推断。Vitis AI 开发环境不仅支持领先的深度学习框架,如 Tensorflow 和 Caffee ,而且还提供全面的 API 进行剪枝、量化、优化和编译训练过的网络,从而可为您部署的应用实现最高的 AI 推断性能。

性能优化的开源库,提供开箱即用的加速,对于采用 C、C++ 或 Python 编写的现有应用而言,代码修改极少,甚至不需要修改代码。按原样利用特定领域的加速库,通过修改适应您的需求,或者在您的自定义加速器中用作算法构建块。

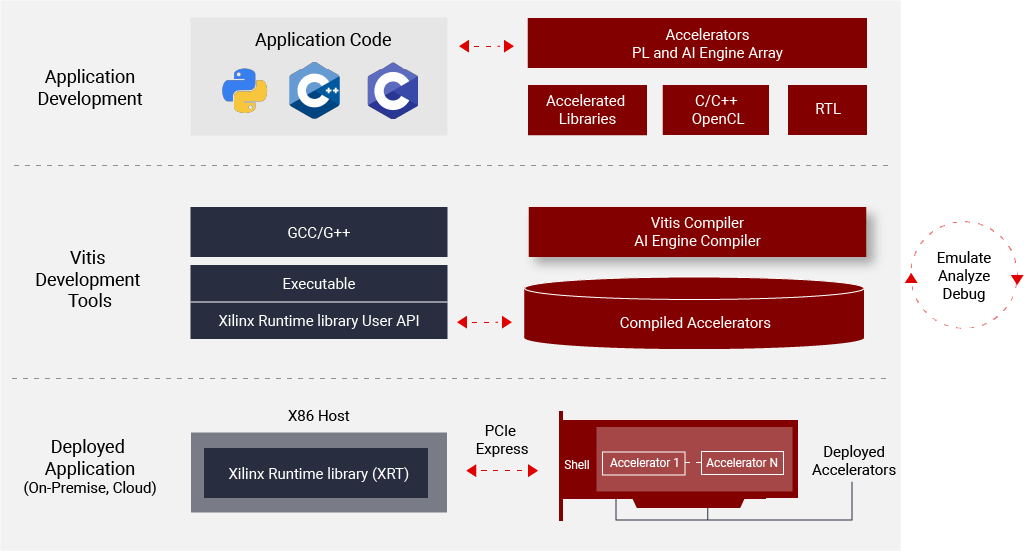

Vitis Core 开发套件

完整的图形和命令行开发工具,其中包括 Vitis 编译器、分析器和调试器,用于构建应用、分析性能瓶颈、调试加速算法,使用 C、C++ 或 OpenCL™ API 进行开发。在您自己的 IDE 中使用这些特性,或者使用独立的 Vitis IDE。

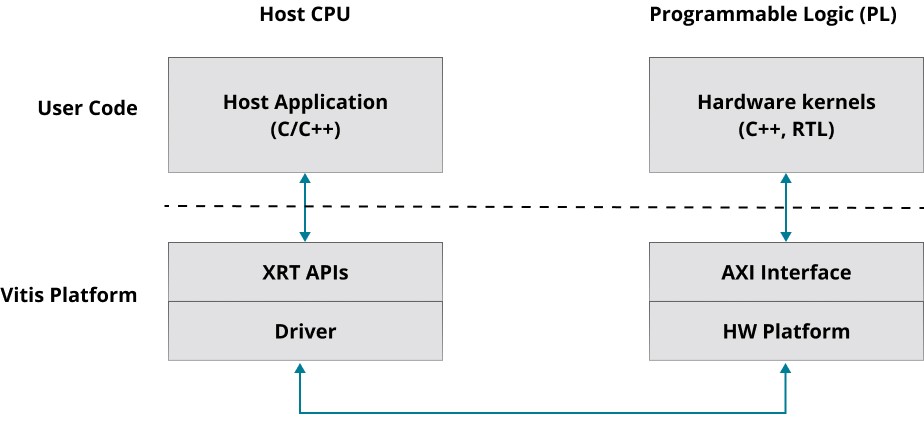

Xilinx RunTime 库

Xilinx Runtime library (XRT) 库旨在促进应用代码(运行在嵌入式 ARM 或 x86 主机上)与加速器(部署在基于 PCIe® 接口的 AMD 加速器卡、基于 MPSoC 的嵌入式平台或自适应 SoC 的可重配置部分上)之间的通信。它包括用户空间库和 API、内核驱动、电路板实用程序和固件。

Vitis 目标平台为 AMD 平台定义了基础软硬件架构及应用环境,包括外部存储接口、自定义输入输出接口和软件运行时。

•对于本地或云的 AMD 加速卡,Vitis 目标平台可自动配置 PCIe 接口,这些接口可连接和管理 FPGA 加速器和 x86 应用代码之间的通信 — 无需实现任何连接细节!

•对于 AMD 嵌入式器件,Vitis 目标平台还包括用于平台上的处理器的操作系统、平台外设的引导加载程序和驱动程序,以及根文件系统。您可以为 AMD 评估板使用预定义 Vitis 目标平台,也可在 Vivado™ Design Suite 中定义自己的 Vitis 目标平台。

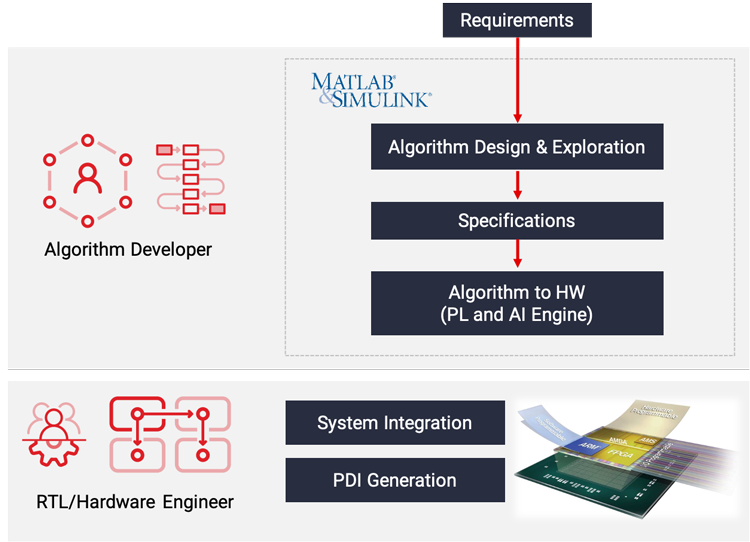

Vitis Model Composer

Vitis Model Composer 是一款面向 MATALB 和 Simulink 环境的 AMD 工具包,支持在 MATALB 和 Simulink 工具中进行快速设计探索和验证,并加速 AMD 器件的量产。

- 使用针对 AI 引擎和可编程逻辑的优化模块,创建设计。可视化仿真结果并对其进行分析,然后将得出的结果与使用 MALTAB 和 Simulink 软件生成的黄金参考进行比较。

- 无缝协同仿真 AI 引擎及可编程逻辑(HLS、HDL)模块。

- 为设计自动生成代码(AI 引擎数据流程图、RTL、HLS C++)及测试台。

- 验证硬件设计,简单易用。

Vitis™ HLS 工具允许用户通过将 C/C++ 函数综合成 RTL,轻松创建复杂的 FPGA 算法。Vitis HLS 工具与 Vivado™ Design Suite(用于综合、布置和布线)及 Vitis™ 统一软件平台(用于所有异构系统设计和应用)高度集成。

- 使用 Vitis HLS 流程,用户可针对 C 代码应用指令,创建专门用于所需实现方案的 RTL。

- 不仅可从 C 语言源代码创建多个设计架构,而且还可启用用于高质量 Correct-by-Construction RTL 的路径。

- C 语言仿真可用于验证设计,支持比基于 RTL 的传统仿真更快的迭代。

- Vitis HLS 工具具有一系列丰富的分析及调试工具,其可促进设计优化。

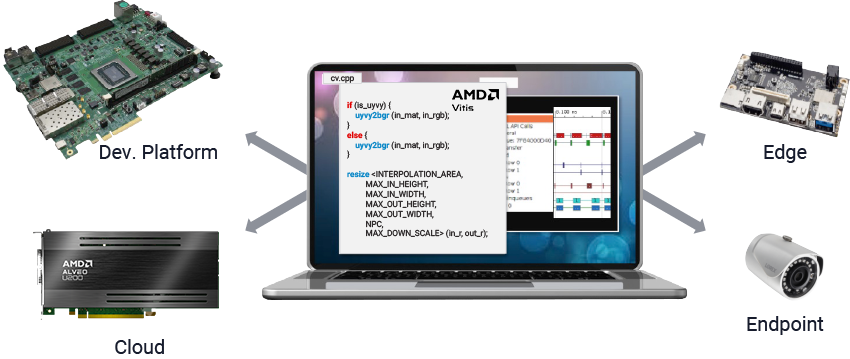

使用 Vitis™ 软件用于应用加速开发流程

为您在边缘、本地或云的数据和计算密集型应用设计加速器:

- 确定应用中需要加速的性能关键部分。

- 使用 Vitis 加速库设计加速器,也可使用 C、C++、OpenCL 或 RTL 开发自己的加速器。

- 构建、分析和调试,以验证功能正确性并验证是否符合性能目标。

- 在边缘、本地或云端的 AMD 平台上部署加速应用

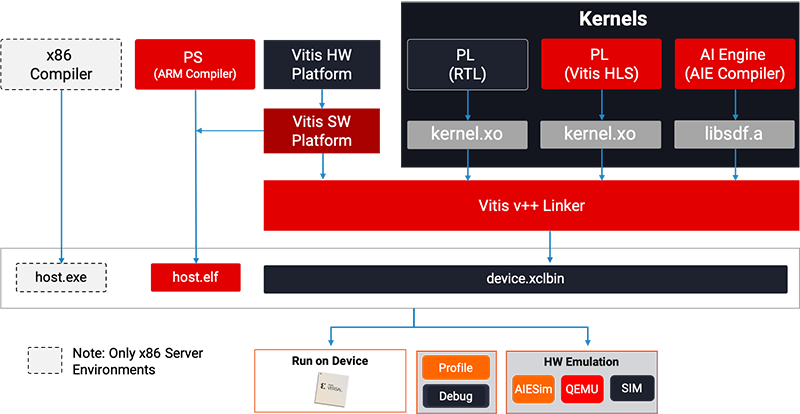

Vitis 支持 PS 或 x86 硬件加速内核,以控制内核。Vitis 应用加速开发流程提供一个框架,用于使用软硬件组件的标准编程语言开发并交付 FPGA 加速应用。对于内核创建,用户可从下面选择:

- 为 PL 内核编写传统 RTL

- 使用 Vitis HLS 为 PL 内核执行 C/C++ 编码

- 面向 PL 和/或 AI 引擎的 Vitis model composer

- 使用 AI 引擎编译器为 AI 引擎执行 C/C++ 编码

此外,Vitis 还支持无 PS 或 x86 的硬件加速内核,以通过控制实现自由运行。自由运行内核没有控制信号端口,不能启停。自由运行内核的“无控制信号”特性会导致以下特征:

- 自由运行内核没有内存输入输出端口,因此只能通过数据流与主机或其它内核(其它内核可能是普通内核,也可能是另一个自由运行内核)互动。

- 当 FPGA 由二进制容器 (xclbin) 编程时,自由运行内核开始在 FPGA 上运行,因此无需主机代码的 clEnqueueTask 命令。

- 当内核开始接收来自主机或其它内核的数据流时,它就开始处理数据流,在没有数据时就停止工作。

使用 Vitis 软件用于应用加速开发流程

Vitis Core 开发套件包括全面的开发工具,可针对 AMD Zynq、MPSoC、RFSoC 和自适应 SoC 器件上的嵌入式处理器设计、调试和部署软件应用。Vitis 嵌入式软件开发特性包括:

- 导入使用 Vivado™ Design Suite 创建的目标平台定义

- 为单处理器、多处理器及异构处理器系统开发应用

- 能够为第三方操作系统创建和配置电路板支持包 (BSP)

- 系统级性能分析与基准测试

- 异构嵌入式系统的实时调试与跟踪

了解更多有关 AMD 嵌入式软件架构 的信息。

Versal AI 引擎开发

AMD VCK5000 Versal™ 开发卡采用 AMD 7nm Versal 自适应 SoC 架构,非常适合 5G、DC 计算、AI、信号处理、雷达等。特定领域的架构可在实现软件可编程性的同时,带来极高的计算能力。使用 AI 引擎将您的应用提升到全新的层面,并使用 Vitis 高层次抽象 API 及其库启动开发。

了解更多有关 VCK5000 的信息 >

AMD Alveo™ 数据中心加速器卡旨在满足现代数据中心不断变化的需求,为常见的工作负载(包括机器学习推断、视频转码和数据库搜索与分析)提供比 CPU 高 90 倍的性能。

Vitis™ 软件开发平台可帮助应用开发者与软硬件开发者等利用 Alveo 加速卡的强大功能来满足其应用对计算、网络和存储的苛刻要求。

选择加速器卡 >

Kria SOM 开发

您现在可以在 AMD Kria SOM 上运行经过认证的 Ubuntu Linux。了解如何在熟悉的 Ubuntu 环境轻松下载、编译、运行和修改选择广泛的 Vitis-AI 示例。

了解更多有关 Kria SOM 的信息>

生活中所产生的数据正不断呈爆炸式增长,因此越来越需要将计算力移到更靠近数据产生的地方,这样才能满足 IIoT、自动驾驶、医学成像及监控等性能关键型应用的响应时间、功耗以及成本目标。

AMD 嵌入式平台正在实现差异化与电源效率都很重要、系统必须非常灵敏而且需要快速部署最新算法及传感器的应用。

浏览 AMD 和合作伙伴边缘平台 >

AMD Varium C1100 卡上的区块链解决方案基于 Vitis 库,是一款创造性的区块链解决方案,集成全球流行的开源软件,其支持 C++ 编程,在 AMD Varium C1100 卡上使用和部署都很便捷。使用 AMD Vitis 工具在 Varium™ C1100 卡上携带区块链解决方案。

了解更多有关 Varium C1000 的信息>

了解更多有关 Vitis 区块链解决方案的信息 >

技术文章:区块链开发 >

Amazon EC2 上的 FPGA

AMD 平台可在降低总体拥有成本的同时,满足现代数据中心工作负载不断变化的需求,如深度学习、视频转码、大数据分析、基因组学、压缩、需要高带宽的网络安全与搜索、增强的网络连接以及通过 CPU 和 GPU 备选方案实现的极高计算能力。

世界各地的所有开发者现在都可通过公共云服务提供商(如 Amazon AWS)广泛访问 AMD FPGA。 使用 Vitis,您可在继续使用熟悉的编程语言(如 C 和 C++)进行开发的同时,在云端充分利用 AMD FPGA 的强大功能。此外,您还可以在更广泛的云计算市场发布您的 FPGA 加速应用,并通过您的解决方案获得盈利。

Vitis 统一软件平台文档

Vitis™ 统一软件平台文档为面向以下两种软件开发流程使用 Vitis 提供支持:应用加速开发和嵌入式软件开发。

Vitis 应用加速开发流程

Vitis 嵌入式软件开发流程.

Vitis HLS 文档

Vitis 加速库文档

Xilinx 运行时库(xrt)文档.

AI 引擎工具和流程用户指南

Ai 引擎内核及图形编程指南.

使用 Vitis™ 统一软件平台设置和加速应用的6个步骤:

下载软件,并查看文档及培训

- 步骤 1:下载 Vitis 核心开发套件

- 步骤 2:下载 Xilinx 运行时库(XRT)

- 步骤 3:从 GitHub 下载 Vitis 加速库

- 步骤 4:下载 Vitis 目标平台文件

- 步骤 5:访问所有 Vitis 文档

- 步骤 6:参加 Vitis 培训课程(课程点播、虚拟课程或课堂)

使用 Vitis 在云端开发

在云端使用 Vitis 统一软件平台开发加速应用,无需本地软件安装,也不需要预先购买所需的硬件平台(即付即用)。立即登录启动开发。

在 AWS 市场使用 FPGA Developer AMI 访问 Vitis 工具。该亚马逊机器实例 (AMI) 包含通过 F1 实例开发、仿真、调试和编译加速算法所需的一切,无需安装本地软件。

- GitHub 上的加速范例

- GitHub 入门教程

- 使用 Vitis 统一软件平台加速应用

- 使用 AMD Alveo 卡加速动态工作负载

- 从 AMD SDK 迁移到 Vitis 嵌入式软件开发 IDE

- 利用 Vitis AI 平台开发 AI 推断解决方案

注: Alveo 目标平台 2020.1 与 Vitis 工具 2020.2 兼容

如需查看有关如何为 Vitis 创建自定义嵌入式目标平台的说明,请参见 Vitis 嵌入式软件开发用户指南 UG1400

Vitis 嵌入式软件开发简介

在 alveo 上的 vitis 加速开发流程(中文), vitis 命令行流程中的 gdb 调试, vitis command line flow 和 vitis analyzer.

- Vitis Unified Software Platform

2023.2 Release Now Available

- Design Tools

The Vitis Software Platform Development Environment

The AMD Vitis™ software platform is a development environment for developing designs that includes FPGA fabric, Arm® processor subsystems, and AI Engines. The Vitis tools work in conjunction with AMD Vivado™ ML Design Suite to provide a higher level of abstraction for design development.

The Vitis software platform includes the following tools:

- Vitis Embedded – For developing C/C++ application code running on embedded Arm processors

- Compiler and simulators – For implementing designs using the AI Engine array

- Vitis HLS – For developing C/C++ based IP blocks that target FPGA fabric

- Vitis Model Composer – A model-based design tool that enables rapid design exploration within the MathWorks Simulink® environment

- A set of open-source, performance-optimized library functions, such as DSP, Vision, Solver, Ultrasound, BLAS, and many more, that can be implemented in FPGA fabric or using AI Engines

Tools & Libraries

Vitis Embedded

Vitis™ Embedded is a standalone embedded software development package for developing host applications running on embedded Arm processors.

Vitis AIE DSP Design Tools

Compilers and simulators.

AMD Versal™ adaptive SoC devices feature AI Engine arrays that enable the implementation of high-performance DSP functions in a resource- and power-optimized manner. Use of AI Engines in conjunction with the FPGA fabric resources can enable very efficient implementation of high-performance DSP applications.

Learn how to use the AMD Vitis tool flow to unlock the hardware acceleration capabilities of AI Engines for DSP applications.

The Vitis HLS tool allows users to easily create complex FPGA algorithms by synthesizing a C/C++ function into RTL.

The Vitis HLS tool is tightly integrated with both Vivado™ ML Design Suite for synthesis and place & route and the Vitis unified software platform for heterogenous system designs and applications.

Vitis Model Composer

Vitis Model Composer is a model-based design tool that enables rapid design exploration within the MathWorks Simulink® environment.

The tool also allows you to model and simulate a design with a mix of AI Engine and programmable logic (HDL/HLS) blocks.

Vitis Libraries

Open-source, performance-optimized libraries that offer out-of-the-box acceleration with minimal to zero code changes to your existing applications, written in C, C++.

Leverage the domain-specific accelerated libraries as is, modify to suit your requirements, or use as algorithmic building blocks in your custom accelerators.

Different Vitis tools must be used to build different portions of AMD adaptive SoCs & FPGAs.

Design Flows

Vitis embedded software development flow.

(Traditionally called Embedded SDK for previous FPGA families)

Export hardware from Vivado as a platform file

Develop application code

Debug and generate boot image

Designers who are developing C/C++ code for the Arm® embedded processor subsystem in AMD adaptive SoCs will typically use this flow.

- Hardware engineers design programmable logic and export the hardware as a Xilinx Support Archive (XSA) file using AMD Vivado™ ML Design Suite.

- Software engineers incorporate this hardware design information in their target platform and use the Vitis Embedded software to develop their application code.

Developers can perform all system-level verification within the Vitis Embedded software and generate boot images to launch the application.

To learn more about the embedded software application development workflow using the Vitis software platform, refer to the Vitis tools for Embedded software development section in the User Guide (UG1400) .

Vitis System Design Flow

(Hardware and Software)

System designers who are integrating both the software and hardware portions of their design in AMD adaptive SoCs will typically use this flow.

This flow is used to develop heterogenous embedded system designs comprising of software applications running on Arm® embedded processors and compute kernels running on programmable logic (PL) and/or Versal™ AI Engine arrays.

This flow comprises:

- A software host application written in C/C++ and typically run on the embedded Arm processor subsystem. It uses the native API implemented by the Xilinx Runtime Library (XRT) to interact with hardware kernels within the AMD device.

- Hardware kernels that can be generated from C++ using the AMD Vitis™ HLS tool or described directly in RTL using AMD Vivado™ ML Design Suite.

To learn more about the heterogenous system design flow using the Vitis unified software platform, refer to the Vitis Tools for Heterogenous System Design section in the user guide (UG1393) .

AMD Alveo™ Data Center accelerator cards employ the same system design flow—the software program runs on an x86 host, and the kernels run in the FPGA on a PCIe®-attached acceleration card. To learn more about the data center acceleration flow using the Vitis unified software platform, refer to the Vitis tools for data center acceleration section in the user guide (UG1393) .

Visit the download page to access the new AMD Vitis™ unified software platform.

What's New

What’s new in 2023.2:.

- New features for AIE-DSP designs – Enhancements to the AIE simulator and compiler

- New standalone Vitis™ Embedded installer – for designers writing embedded C code for the PS subsystem

- New Vitis Unified IDE (GUI) – Starting with 2023.2, Vitis features a new common GUI across all the Vitis tool. Vitis Unified Integrated Design Environment (IDE) .

- New features for profile, debug & trace – for the AMD Versal™ AIE device family

For more details, visit our Whats New page.

Documentation

- Vitis Unified Software Platform Tutorials

- Vitis Embedded Software Development User Guide (UG1400)

- Vitis Unified Software Platform (UG1393)

- Accelerating Applications using Vitis Unified Software

- Migrating from AMD SDK to Vitis Embedded Software Development

- Github Tutorials

- Developer Series Webinar

Community Forums

- Vitis Acceleration

- AI Engine Architecture Tools

Xilinx Vitis HLS 2020.1 beta 初体验(一)

防秒退提醒:本文比较了基于现有 Vivado HLS 2019.2 和最新版本的 Vitis HLS 2020.1 的硬件设计步骤来看 Xilinx 在 HLS 上最近的进展。本文(一)初步测试了新版 Vitis HLS 中声称的自动优化代码的功能。

在今年的 FPGA2020 会议上,Xilinx 宣布 Vitis HLS 的前端将开源。用户之前只能通过 C/C++ 作为输入代码,来生成 Verilog/VHDL 在 FPGA 上运行,期间不能对综合过程进行干涉。而前端的开源将意味着,从 C 到 Verilog 的过程中,多了一个可以定制优化的选项。用户可以将 C 先编译成 LLVM IR(一种类似汇编的中间语言),然后自制 LLVM pass 对输入代码进行分析或者优化,然后将改进的 LLVM IR 送入 Vitis HLS 后端生成更高效的 Verilog。

这样的好处是在 HLS 领域,很多工具都是基于 LLVM 开发的:先从 C/C++ 生成 LLVM IR,再在 LLVM IR 层进行优化,然后将 LLVM IR 调度称时序电路输出 RTL。那么用户以后如果想要在 Vitis HLS 里综合出更好的电路,可以自己定制或者从网上下载别人设计好的 LLVM pass 插件在 LLVM IR 的层面进行进一步自动优化。

几周前我收到了来自 Xilinx 团队的 Vitis HLS 2020.1 beta 版本。但是由于比较忙一直没有打开过,最近终于有时间体验一波,顺便跟大家分享一下。

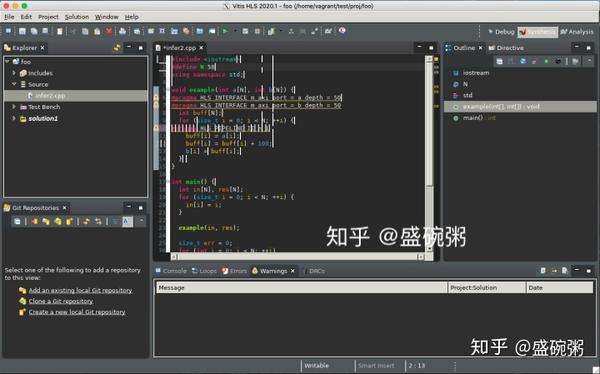

1. GUI 用户界面

界面终于有 dark mode 了,不喜欢的也可以在偏好里面调回 light mode。

在我收到的压缩文件中,Xilinx 团队提供了一个以下一个例子。我将用 Vivado HLS 2019.2 来比较新版的 Vitis HLS 发生了哪些变化。(以下假设大家有用过 Vivado HLS,所以很基础的我就不提了,比如 pragma 是什么或者报告的每一项是什么。这里我只提具体的变化。如果大家需要更纤细简单的 Viavdo HLS 教程请在下方留言。)

Vivado HLS 2019.2

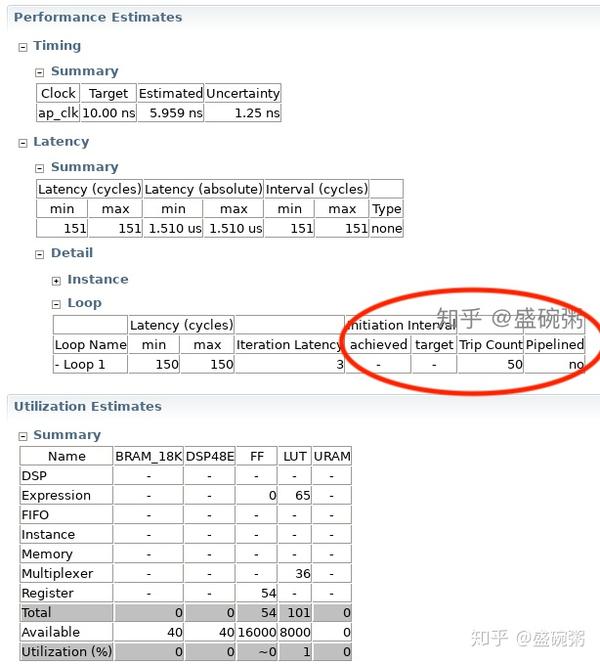

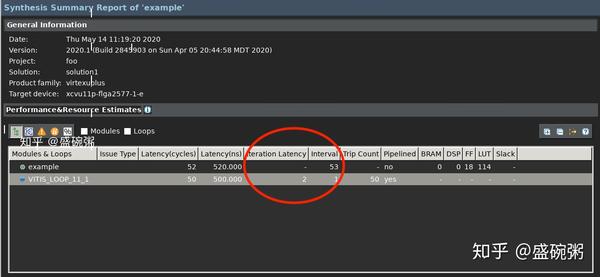

那么如果在 Vivado HLS 2019.2 里面跑, 不做任何优化 ,得到的综合结果是这样的:

我们可以在报告中看到,一个循环执行了3个时钟周期,加上开始的一个周期,总共执行了151个周期。而且因为没有设置任何的输入输出的协议,Vivado HLS 采用了默认的 block interface 来对函数进行综合,得到以下接口(VHDL 直接把类在定义里面标好了,多友好):

那么高度用户就会 设置流水线 和 优化接口 ,在代码中加入 pragma:

那么输出的报告就会变为:

因为流水线的原因,II 变为了 1,吞吐量提速3倍,但是采用了 AXI4 的接口,读写外部数据的延迟增加了十几个时钟周期,所以总提速2.35倍。然后再看生成的 RTL,接口被定制成了 AXI 协议。

小结: 在 Vivado HLS 2019.2 中,代码的可综合性已经比较高,但是默认优化十分有限,用户需要对硬件设计有一定的了解,才能让综合出来的代码实现期望中的高性能。

Vitis HLS 2020.1

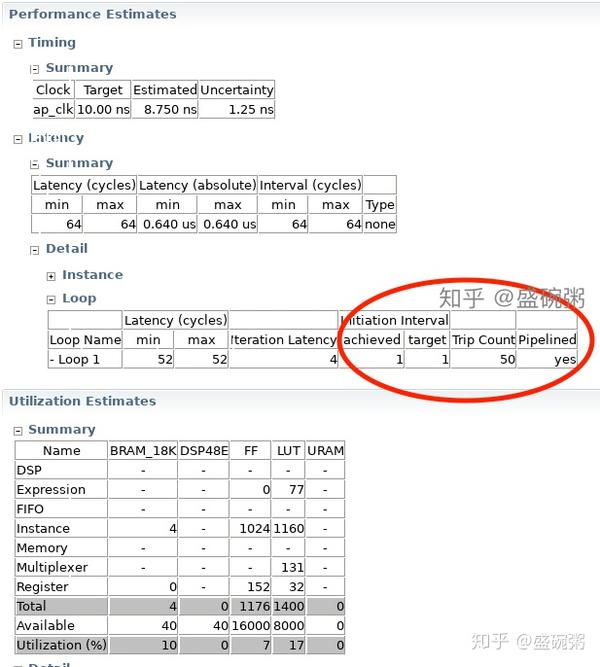

而在新版的 Vitis HLS 2020.1 中,官方称原来没有任何优化 directive 的代码会被编译器进行自动分析和优化,用户不必在逐步添加一些很明显需要的优化来达到最优。现在我来尝试一下,得到的结果是:

从上图我们可以看到,Vitis HLS 对函数中的循环进行了自动流水线化,得到了 II 为1。但是并没有对接口协议进行优化,所以 RTL 的接口还是和之前 Vivado HLS 默认的一样:

此处我的猜测是因为编译器无法判断该代码是 FPGA 直接与 DDR 交互还是访问相同 FPGA 片上的数据,所以无法给出优化方案。

- 相较于 Vivado HLS 来说,Vitis HLS 多了一块自动优化的功能,但是目前来说还是非常有限。不过也可能是这个例程过于简单,如果运行大型工程可能会发现更多的功能。合理猜测 更多的自动优化功能会在后期逐步开放,在开源的 LLVM 中由官方和用户共同开发。

- 从核心设计角度来说,后端内核应该变化不大,静态调度的死穴尚未解决。

以上是关于新版 Vitis HLS 的自动优化测试, 下一篇我将给大家带来如何将 LLVM 前端嵌入 Vitis HLS 的笔记 。如果大家对与新版 Vitis HLS 有什么问题或者看法可以留在评论下方或者私信,我有空尽量在软件里验证。

oscarkramer (Member) asked a question.

- Vitis Acceleration & Acceleration

hongh (AMD)

Diwen (Member)

oscarkramer (Member)

Related Questions

Community Feedback?

Countdown to 2025 RODEOHOUSTON |

March 4 - 23, 2025.

HOW TO BECOME A

RODEO VOLUNTEER

JOIN MORE THAN 35,000 VOLUNTEERS SERVING ON 110 COMMITTEES.

2024 LIVESTOCK SHOW

AUCTION RESULTS

TEXAS 4-H AND FFA STUDENTS GET REWARDED FOR THEIR HARD WORK YEAR-ROUND.

Educational

Since 1932, more than $600 million has been awarded to texas youth

OFFICIAL RODEO MERCHANDISE

Katie kime pj set.

$120.00 USD

Ladies Sleeveless Polo

Leather rocks glass set, brook boots wine tote.

$180.00 USD

HLSR White Bow-H Polo

1932 flag flat bill, latest news, the houston livestock show and rodeo announces 2025 dates, rodeohouston® athletes claim championship victory and $50,000 prize, inaugural class inducted into rodeohouston® hall of fame, ag mechanics grand and reserve champions announced, leon coffee to return in new role in 2025 after 31 years in the barrel for rodeohouston®, 2024 houston livestock show and rodeo™ junior market steer auction results, 2024 grand champions selected at junior market steer show, rodeohouston headlines | wild card 1, pinch ‘n twist crawfish boil & catfish fry, oh, boy oh, boil, brisket & pork butt sale, 2024 crawfish boil, kentucky derby party, scramble for scholarships golf tournament, swinging for scholars golf tournament, crawfish cook-off, cornhole & crawfish bash, mission statement.

The Houston Livestock Show and Rodeo™ promotes agriculture by hosting an annual, family-friendly experience that educates and entertains the public, supports Texas youth, showcases Western heritage and provides year-round educational support within the community.

AGRICULTURE

Western heritage, entertainment, meet our scholars.

Samantha W. 2021 FFA Scholarship Winner

Evelyn L. 2022 Houston Area Scholarship Winner

Cameryn J. 2021 4-H Scholarship Winner

RODEOHOUSTON

Rodeohouston® super series.

A 20-day tournament-style competition that crowns an event champion in bareback riding, bull riding, saddle bronc riding, steer wrestling, tie-down roping, team roping, and women’s barrel racing and breakaway roping

Athlete Payout

Total: $2,178,000 Champions: $50,000 + previous round winnings Winnings: Custom-made saddle and belt buckle + an invitation to compete at RODEOHOUSTON the following two years

HERITAGE PARTNERS

- Skip to Content

- Skip to Main Navigation

- Skip to Search

Indiana University Bloomington Indiana University Bloomington IU Bloomington

- Staff Advisory Board

- Departments, Centers & Institutes

- Our Founding Spirit

- Richard G. Lugar

- Founding Dean

- Dean's Advisory Council

- Majors, minors & more

- Certificates

- Dual Degrees

- Minors & Certificates

- Student Portal

- Foreign Language Studies

- HLS Esade Exchange

- HLS Leiden Exchange

- HLS Waseda Exchange

- Peace Corps Prep

- HLS Student Portal

- Academic Advising

- Nancy and Michael Werner Fellowship in Latin American Studies

- FLAS Fellowships

- Tips for undergraduates

- Visit Information

- Frequently Asked Questions

- Engaged Learning

- HLS Global Development Consulting

- Student Ambassadors

- Global Student Seven (GS7)

- Student Organizations & Activities

- Sigma Iota Rho (SIR)

HLS Living-Learning Center

- Building Careers in International Development

- Global Leaders & Professionals Program

- HLS Professional Mentor Program

- Emerging Leaders Council

- Internships

- Recent Grads, Recently Hired

- NTT Faculty Criteria

- Standing Committees

- News & Events

- Hamilton Lugar Mentor Collective

- Global Scholars Leadership Program

- Alumni Stories

- America's Role in the World®

Hamilton Lugar School of Global and International Studies

John Ciorciari named dean of Hamilton Lugar School

Incubating Ideas to Ignite Change

The Hamilton Lugar School of Global & International Studies at Indiana University is a leader in the study of international affairs. We make the world a better place by engaging with its governments, businesses, laws, and nonprofit sectors, and we pursue innovations and solutions from the strong foundation of a Big Ten research university.

The first step to changing the world is seeking to understand it. We’ll teach you how. HLS offers nearly 20 undergraduate majors and minors, more than 50 graduate and doctoral opportunities, and more than 300 study abroad programs. You’ll graduate fluent in at least one of the 80+ languages taught on campus and equipped with the tools necessary to make an impact on the world.

- Undergraduate Programs

Complete an international relations degree with any of our 6 majors, 9 minors, and 6 certificate programs, or combine your HLS studies with any other IU program across our several colleges and schools for an interdisciplinary learning experience tailored to your goals.

- Graduate Programs

Expand your professional competencies and reach new possibilities in your career through nearly 50 master’s, doctoral, and certificate programs at HLS. You can also double your prospects with a dual degree, including an MPA, MBA, or JD, through IU’s other professional schools.

Request info

Explore academic programs.

Pair our majors and minors with language programs and more than 200 fields of study

Plan a visit

Sign up for a personalized, virtual visit with our recruitment team

Find admissions information for nearly 20 undergraduate majors, minors, and certificates, and 50 graduate pathways.

Driving Passions with Expertise

Our undergraduate, graduate, and certificate programs open realms of possibility and discovery. You can pursue direct involvement in foreign policy or combine a HLS program with any other IU major to prepare for the exact career that drives your passion.

Expert faculty bring their passion as mentors and thinkers to each major and minor, master’s and doctoral program, and language and professional certificate. They are scholars on human rights and climate change studies, linguists and sociologists, former humanitarian aid workers and diplomats. These teachers and doers are proud to represent an international affairs school and to foster the next generation of international policy-makers.

Embrace the challenge

“The world has always been of interest to me. Whether that was excelling in my Spanish classes and diving into Latin American cultures, learning about the colonial French roots of my parents’ home country of Guinea, or researching my religion and how the Arabian Peninsula influenced it.”

Ramatou Soumare

International Law and Institutions, class of 2022; Ramatou gave the student introduction for Mayor Pete Buttigieg’s foreign policy speech at the IU Auditorium in June 2019.

Speaking Globally

We teach more languages than any other university in the United States, with more than 80 program offerings from regions across the globe. We are distinct among international relations schools for our dedication to deep cultural fluency and our broad scope of cultural investment, from Arabic to Mongolian to Zulu.

Opportunities Outside the Classroom and Country

Indiana University stands out among international affairs colleges for its bustling student organizations, clubs, and service learning projects that bring degrees in global studies and international politics out of the classroom and into everyday life. You can also take your learning to more than 52 countries through IU’s study abroad programs.

Set the standard

#1 Number of foreign languages taught in the US

#1 Available Foreign Language & Area Studies Fellowships

70% Undergraduate students travel abroad

Launching Your Career

From your earliest days on campus, you will have access to career development workshops and programs dedicated to your professional prospects. We offer one-on-one coaching, a mentoring program, and events with experts, recruiters, and HLS alumni. You can earn a competitive internship and carry your international politics degree into an impactful career with organizations like the United Nations, the Peace Corps, and the US Department of State.

Follow Your Future at HLS

We are committed to supporting and empowering your journey at Indiana University. Let us know how we can help nurture your world-changing ideas ; once you’re here, we will equip you with the knowledge and expertise to put them into action.

#1 Language Flagship programs in the US

#2 Boren Scholars

Top 16 Fulbright Scholars

Train on the world stage

"I’ve had the opportunity to intern with the U.S. Department of State at the US Consulate in Guangzhou, China and studied abroad in Seoul, South Korea at Yonsei University. I also had the opportunity to attend the 63rd session of the United Nations Commission on the Status of Women with Professor Shruti Rana as a student delegate. I was also one of the first students to switch my major to International Law and Institutions. This joint degree between the Hamilton Lugar School and the Maurer School of Law helps students like me develop the expertise needed to make an impact after graduation."

Kimber Garland

International Law, East Asian Languages & Cultures and International Law & Institutions, class of 2020

Join our community of scholars, practitioners, leaders & learners

Language Flagship Programs

The Hamilton Lugar School houses Language Flagship programs in Arabic and Chinese (Mandarin). Indiana University is home to three programs, the most in the country.

The LLC is a close-knit residential community for globally minded students who take part in a tailored program of activities that bridge the classroom with the world.

Financial aid

School-, university-, and government-funded financial aid is available for tuition, Scholarships funded by the school, university, and government are available for tuition, internships, and study abroad.

Growing up in Indiana, one learns early on that talent and accomplishments count—but honesty and integrity count more. Sen. Richard Lugar

Recent HLS News

Hamilton on Foreign Policy #239: Justice O’Connor championed civics education

John Ciorciari named dean of the Hamilton Lugar School of Global and International Studies

Hamilton on Foreign Policy #238: Big decisions and American history

Authoritative new research by Professor Asma Afsaruddin uncovers deep insights into Islam and women’s agency in Muslim-majority societies

Hamilton on Foreign Policy #237: Foreign policy rises in public attention

Finals Fun Fest

Global Learning Showcase

11:30 a.m. — 1 p.m.

Ferguson International Center

Ostrom Workshop | Water Governance Working Group

10 a.m. — 11 a.m.

Social Entrepreneurship on the Tibetan Plateau

Starts at 3:30 p.m.

Global & International Studies Building

Land acknowledgement

The Hamilton Lugar School wishes to acknowledge and honor the Miami, Delaware, Potawatomi, and Shawnee people, on whose ancestral homelands and resources Indiana University was built.

Want to learn more?

Are you ready, hamilton lugar school of global and international studies social media channels, contact, address and additional links, for students.

- Career Development

- Scholarships

- Study Abroad

- Student Clubs

- Student Resources

For Faculty/Staff

- Communications Support

- Digital Slides

- Faculty & Staff Intranet

- Request Forms

HAMILTON LUGAR SCHOOL BLOOMINGTON

Xilinx Vitis HLS introduction

Table of Contents

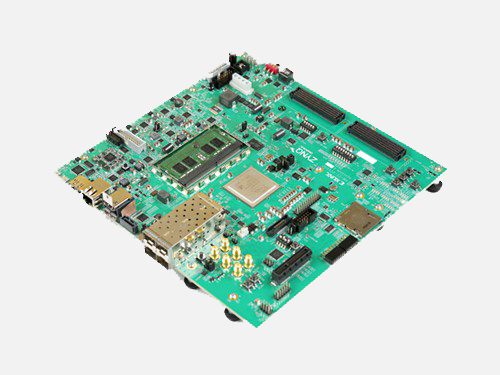

Xilinx Vitis HLS (formerly Xilinx Vivado HLS) is a High-Level Synthesis (HLS) tool developed by Xilinx and available at no cost. Vitis HLS allows the user to easily create complex FPGA-based algorithms using C/C++ code. It supports complex data types (floating-points, fixed-points,…) and math functions (sine, arctan, sqrt,…). It also supports AXI4-Stream to easily exchange data with other IPs.

This tools is particularly useful when porting a control algorithm from the CPU to the FPGA of a power converter controller such as the B-Box RCP , the B-Board PRO .

Alternative to Xilinx Vitis HLS

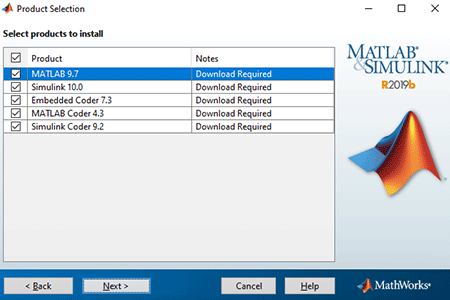

An alternative to Vitis HLS is Model Composer , which provides the same features in a MATLAB Simulink environment. For “lower-level” designs such as PWM modulators, tools such as System Generator or HDL Coder are more appropriate.

Compared to Model Composer, Vitis HLS presents the advantage of being standalone and free of cost. However, Vitis HLS may be more difficult to use, as it requires some C++ skills. Moreover, it is much more tedious to write testbenches for Vivado HLS designs.

Downloading and installing Xilinx Vitis HLS

Xilinx Vitis HLS is installed alongside Vivado, as details in the installing Vivado Design Suite page.

Xilinx Vitis HLS example workflow

This tutorial broadly outlines the main steps required to generate a Vivado IP using Vitis HLS. It is not its purpose to be exhaustive but rather serves as a guideline. It also provides tips for designs targetting imperix controllers. For more detailed information, the user should refer to the Xilinx documentation, such as:

- The High-Level Synthesis Tutorial (xilinx.com)

- Getting Started with Vitis HLS (github.com)

- Xilinx HLS basic examples (github.com)

The sources of this Xilinx Vitis HLS example can be downloaded below.

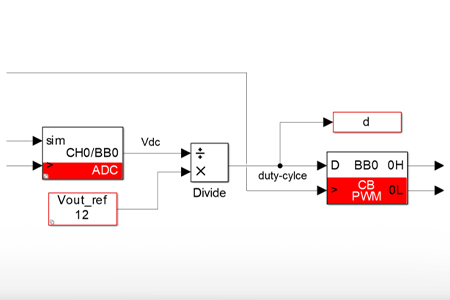

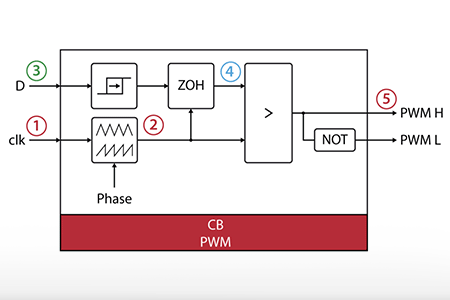

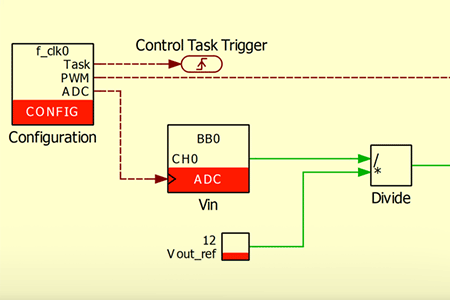

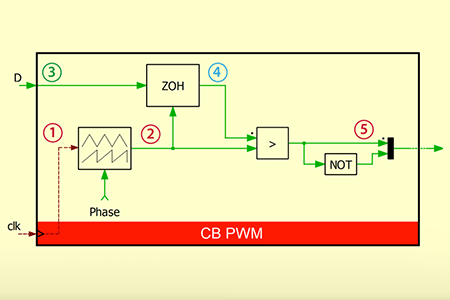

The tutorial uses a PI-based current control implementation as an example to illustrate the key points of the Xilinx Vitis HLS workflow. It is based on the Forward Euler method, which is presented on the PI controller implementation for current control technical note.

It is highly recommended to read through the high-Level synthesis for FPGA developments page to see how this IP integrates into a complete design. It will help to understand some of the choices made, notably concerning the input and output ports.

Creating a xilinx Vitis HLS project

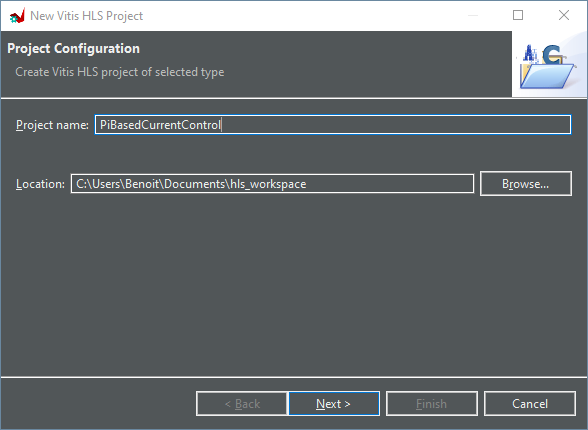

1. Launch Xilinx Vitis HLS (the following screenshots comes from Vitis HLS 2020.2) 2. Click on Create Project or go to File -> New Project… 3. Enter a project name and hit Next

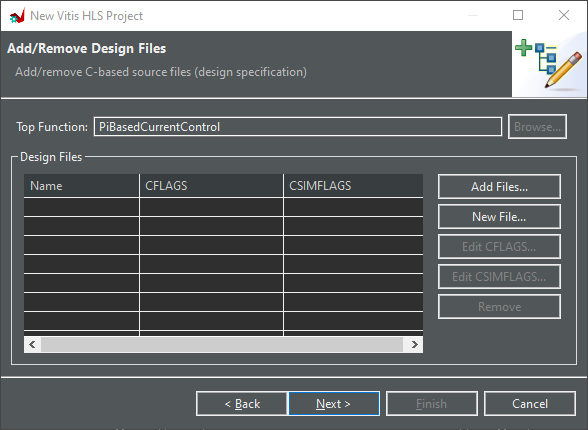

4. Chose a top function name. This will also be the name of the resulting Vivado IP. Hit Next

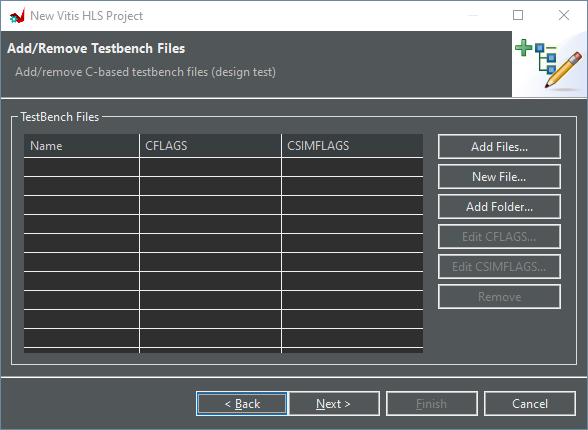

5. There is no need to select a testbench file at this stage. Hit Next.

6. Setup the clock period of 4 ns . Select the part xc7z030fbg676-3 , keep Vivado IP Flow Target for the Flow Target, and hit Finish .

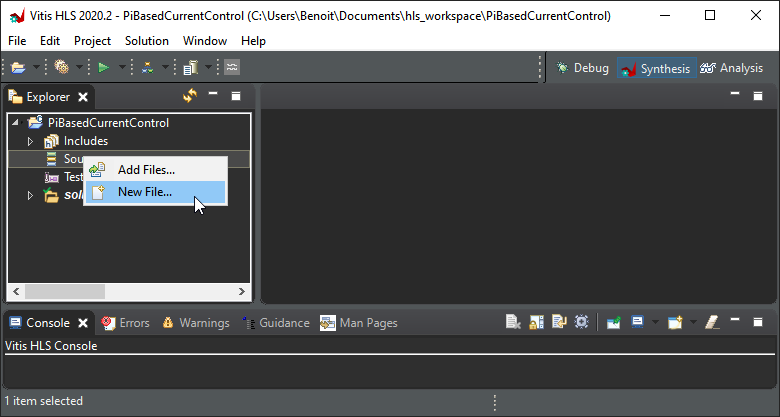

7. Add sources the C++ source files to the project. In this example, we add the sources PiBasedCurrentControl.cpp and PiBasedCurrentControl.h . These files are available in the zip provided above.

Below is the C++ code of the algorithm used in this example, for reference. Each portion of this code is explained and commented on in the following sections.

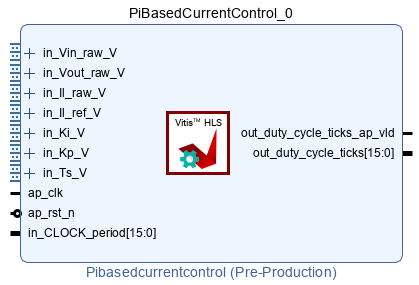

Defining the IP input and output ports

The code below defines the inputs and outputs of the IP. We made the following choices:

- The parameters coming from the CPU ( Il_ref , Kp and Ki ) are set as single-precision (float).

- The inputs Il_raw , Vin_raw and Vout_raw will be directly connected to the ADC interfaces and as such must be set as int16 .

- The input Ts is a uint32 value holding the sampling time in nanoseconds.

- The input CLOCK_period is a uint16 value representing the PWM period in ticks.

- The output duty_cycle_ticks is a uint16 value that will be connected to the PWM IP.

- After the user CPU code starts, the CLOCK_period input is constant. Thus its mode is set as ap_none (No protocol).

- The duty_cycle_ticks output uses the ap_vld (Valid Port) mode. As shown on the very last image of this page, it will generate an additionnal “valid” port duty_cycle_ticks_ap_vld indicating when the duty_cycle_ticks can be read.

- All the other inputs use the AXI4-Stream protocol.

Implementing the algorithm

The algorithm implemented in this example is the same as the one in the Model Composer introduction . Taking a look at that page may help to understand the algorithm.

The read() method reads one value from an AXI4-Stream. The algorithm starts by reading all the stream inputs. The Ts input is multiplied by 1e-9 to obtain a value in seconds.

The ADC values provided by the starter template are the raw result from the ADC chips. They must be multiplied by a gain to obtain physical values. An example of gain computation is available on the ADC block help page. To simplify the model, the ADC gains are defined as constants and offsets are simply ignored. This example considers the sensor sensitivities of a PEB 8038 module. The user could choose to use tunable parameters coming from the CPU so that the ADC can be tuned in real-time.

The integrator of the PI controller acts as an accumulator and, thus, requires that its value is kept in memory between executions. To that end, the static keyword must be used. The HLS RESET pragma specifies that this variable is reset when the IP block reset input pin ( ap_rst_n ) is asserted.

By design, the duty_cycle ranges from 0.0 to 1.0. Such a narrow range is particularly well-suited for a fixed-point algorithm, as we know beforehand that only a single bit is required for the integer part. We arbitrarily choose a fractional length of 15 bits so we obtain a fix16_1 5 value. Since the output is a number of ticks , it must be an integer value, and the fractional part is removed by simply transforming the result into a uint16 .

Generating an IP core using Vitis HLS

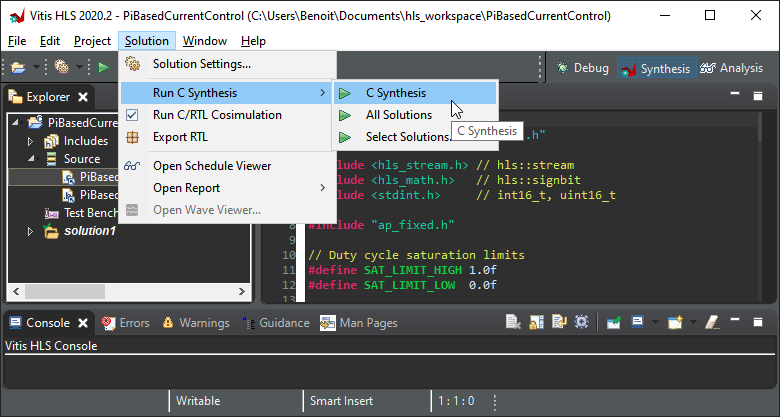

- Launch the C Synthesis by going to Solution -> Run C Synthesis -> Active Solution

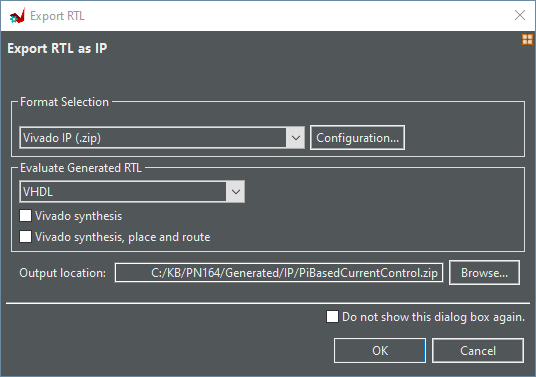

- Click Solution -> Export RTL ,

- Select the Vivado IP (.zip) format.

- The generated RTL can be VHDL or Verilog, it does not matter.

- Choose an output location, for instance C:/KB/PN163/Generated/IP ,

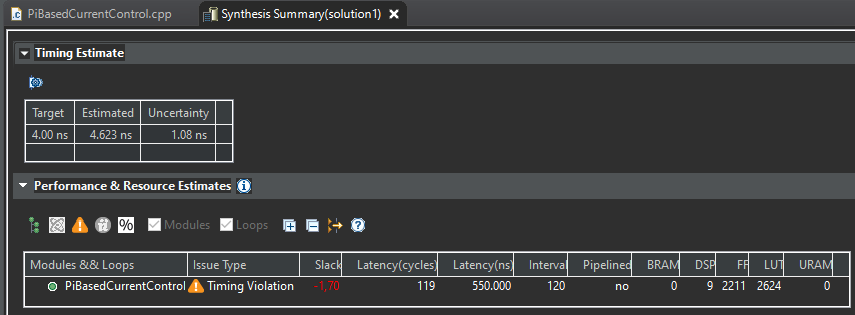

Performance and resource estimates

The FPGA of imperix controllers (part: xc7z030fbg676-3) possesses 78600 LUT, 157200 FF and 400 DSP, from which around ~30% is used by the imperix firmware IP. By clicking on Solution -> Open Report -> Synthesis, the user has access to the synthesis summary report which estimates the IP latency and resource usage. In this example, Vitis HLS shows the following estimation: 2624 LUT (3.3% of total), 2211 FF (1.4%), and 9 DSP (2.3%).

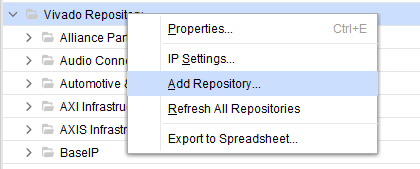

Adding the IP core in a Vivado project

Here are the steps required to add the example IP generated by Xilinx Vitis HLS into a Vivado project.

- Unzip the file generated by Xilinx Vitis HLS (PiBasedCurrentControl.zip),

- Go in the IP Catalog,

- Right-click and select Add Repository…

- Select the folder containing your unzipped IP (e.g. C:\imperix\sandbox_sources\my_IPs ). This folder can contain multiple IPs.

- And finally the IP can be added to a block design like any other Xilinx IP

To see an example where the PI-based current control IP in action please refer to the high-Level Synthesis for FPGA developments page.

Benoit is the head of software development. On the knowledge base, he is the author of numerous software reference documents.

Similar Posts

Installation guide for imperix ACG SDK

This note gives step-by-step instructions to install the Software Development Kit (SDK) for the Automated Code Generation (ACG) from Simulink or PLECS. A general overview…

Getting started with ACG SDK on Simulink

This note introduces basic instructions in order to efficiently get started with the imperix ACG SDK on Simulink. A general overview of software-related notes is…

Simulation essentials with Simulink

This note provides in-depth content for an accurate and efficient offline simulation of an imperix controller and the corresponding plant model using ACG SDK on Simulink. A…

Getting started with ACG SDK on PLECS

This note gives the instructions to efficiently get started with the imperix ACG SDK on PLECS. A general overview of software-related notes is given on this…

Simulation essentials with PLECS

This note provides in-depth content for an accurate and efficient offline simulation of an imperix controller and the corresponding plant model using ACG SDK on…

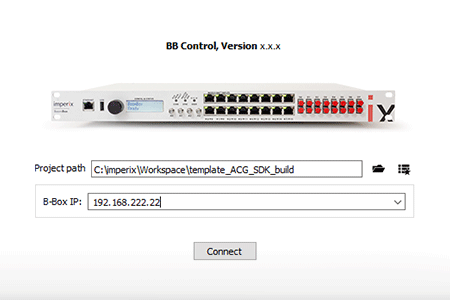

Getting started with BB Control

This note explains how to build, load, and execute the control code that is generated from Simulink, PLECS or imperix IDE (C/C++ code). It notably…

Navigation Menu

Search code, repositories, users, issues, pull requests..., provide feedback.

We read every piece of feedback, and take your input very seriously.

Saved searches

Use saved searches to filter your results more quickly.

To see all available qualifiers, see our documentation .

- Notifications

HLS.js is a JavaScript library that plays HLS in browsers with support for MSE.

video-dev/hls.js

Folders and files, repository files navigation.

HLS.js is a JavaScript library that implements an HTTP Live Streaming client. It relies on HTML5 video and MediaSource Extensions for playback.

It works by transmuxing MPEG-2 Transport Stream and AAC/MP3 streams into ISO BMFF (MP4) fragments. Transmuxing is performed asynchronously using a Web Worker when available in the browser. HLS.js also supports HLS + fmp4, as announced during WWDC2016 .

HLS.js works directly on top of a standard HTML <video> element.

HLS.js is written in ECMAScript6 ( *.js ) and TypeScript ( *.ts ) (strongly typed superset of ES6), and transpiled in ECMAScript5 using Babel and the TypeScript compiler .

Rollup is used to build the distro bundle and serve the local development environment.

- DVR support on Live playlists

- Fragmented MP4 container

- ITU-T Rec. H.264 and ISO/IEC 14496-10 Elementary Stream

- ITU-T Rec. H.265 and ISO/IEC 23008-2 Elementary Stream

- ISO/IEC 13818-7 ADTS AAC Elementary Stream

- ISO/IEC 11172-3 / ISO/IEC 13818-3 (MPEG-1/2 Audio Layer III) Elementary Stream

- ATSC A/52 / AC-3 / Dolby Digital Elementary Stream

- Packetized metadata (ID3v2.3.0) Elementary Stream

- AAC container (audio only streams)

- MPEG Audio container (MPEG-1/2 Audio Layer III audio only streams)

- Timed Metadata for HTTP Live Streaming (ID3 format carried in MPEG-2 TS, Emsg in CMAF/Fragmented MP4, and DATERANGE playlist tags)

- AES-128 decryption

- "identity" format SAMPLE-AES decryption of MPEG-2 TS segments only

- FairPlay, PlayReady, Widevine CDMs with fmp4 segments

- Level capping based on HTMLMediaElement resolution, dropped-frames, and HDCP-Level

- CEA-608/708 captions

- WebVTT subtitles

- Alternate Audio Track Rendition (Master Playlist with Alternative Audio) for VoD and Live playlists

- Instant switching (immediate quality switch at current video position)

- Smooth switching (quality switch for next loaded fragment)

- Bandwidth conservative switching (quality switch change for next loaded fragment, without flushing the buffer)

- In Auto-Quality mode, emergency switch down in case bandwidth is suddenly dropping to minimize buffering.

- Accurate Seeking on VoD & Live (not limited to fragment or keyframe boundary)

- Ability to seek in buffer and back buffer without redownloading segments

- All internal events can be monitored (Network Events, Video Events)

- Playback session metrics are also exposed

- Retry mechanism embedded in the library

- Recovery actions can be triggered fix fatal media or network errors

- Redundant/Failover Playlists

- HLS Variable Substitution

Supported HLS tags

For details on the HLS format and these tags' meanings, see https://datatracker.ietf.org/doc/html/draft-pantos-hls-rfc8216bis

Multivariant Playlist tags

- #EXT-X-STREAM-INF:<attribute-list> <URI>

- #EXT-X-MEDIA:<attribute-list>

- #EXT-X-SESSION-DATA:<attribute-list>

- #EXT-X-SESSION-KEY:<attribute-list> EME Key-System selection and preloading

- #EXT-X-START:TIME-OFFSET=<n>

- #EXT-X-CONTENT-STEERING:<attribute-list> Content Steering

- #EXT-X-DEFINE:<attribute-list> Variable Substitution ( NAME,VALUE,QUERYPARAM attributes)

The following properties are added to their respective variants' attribute list but are not implemented in their selection and playback.

- VIDEO-RANGE (See #2489 )

Media Playlist tags

- #EXT-X-VERSION=<n>

- #EXTINF:<duration>,[<title>]

- #EXT-X-ENDLIST

- #EXT-X-MEDIA-SEQUENCE=<n>

- #EXT-X-TARGETDURATION=<n>

- #EXT-X-DISCONTINUITY

- #EXT-X-DISCONTINUITY-SEQUENCE=<n>

- #EXT-X-BYTERANGE=<n>[@<o>]

- #EXT-X-MAP:<attribute-list>

- #EXT-X-KEY:<attribute-list> ( KEYFORMAT="identity",METHOD=SAMPLE-AES is only supports with MPEG-2 TS segments)

- #EXT-X-PROGRAM-DATE-TIME:<attribute-list>

- #EXT-X-SERVER-CONTROL:<attribute-list>

- #EXT-X-PART-INF:PART-TARGET=<n>

- #EXT-X-PART:<attribute-list>

- #EXT-X-SKIP:<attribute-list> Delta Playlists

- #EXT-X-RENDITION-REPORT:<attribute-list>

- #EXT-X-DATERANGE:<attribute-list> Metadata

- #EXT-X-DEFINE:<attribute-list> Variable Import and Substitution ( NAME,VALUE,IMPORT,QUERYPARAM attributes)

- #EXT-X-GAP (Skips loading GAP segments and parts. Skips playback of unbuffered program containing only GAP content and no suitable alternates. See #2940 )

The following tags are added to their respective fragment's attribute list but are not implemented in streaming and playback.

- #EXT-X-BITRATE (Not used in ABR controller)

Parsed but missing feature support

Not Supported

For a complete list of issues, see "Top priorities" in the Release Planning and Backlog project tab . Codec support is dependent on the runtime environment (for example, not all browsers on the same OS support HEVC).

- HLS Interstitials

- #EXT-X-I-FRAME-STREAM-INF I-frame Media Playlist files

- "identity" format SAMPLE-AES method keys with fmp4, aac, mp3, vtt... segments (MPEG-2 TS only)

- MPEG-2 TS segments with FairPlay Streaming, PlayReady, or Widevine encryption

- FairPlay Streaming legacy keys (For com.apple.fps.1_0 use native Safari playback)

- MP3 elementary stream audio in IE and Edge (<=18) on Windows 10 (See #1641 and Microsoft answers forum )

Server-side-rendering (SSR) and require from a Node.js runtime

You can safely require this library in Node and absolutely nothing will happen . A dummy object is exported so that requiring the library does not throw an error. HLS.js is not instantiable in Node.js. See #1841 for more details.

Getting started with development

First, checkout the repository and install the required dependencies

The dev server will host files on port 8000. Once started, the demo can be found running at http://localhost:8000/demo/ .

Before submitting a PR, please see our contribution guidelines . Join the discussion on Slack via video-dev.org in #hlsjs for updates and questions about development.

Build tasks

Build all flavors (suitable for prod-mode/CI):

Only debug-mode artifacts:

Build and watch (customized dev setups where you'll want to host through another server - for example in a sub-module/project)

Only specific flavor (known configs are: debug, dist, light, light-dist, demo):

Note: The "demo" config is always built.

NOTE: hls.light.*.js dist files do not include alternate-audio, subtitles, CMCD, EME (DRM), or Variable Substitution support. In addition, the following types are not available in the light build:

- AudioStreamController

- AudioTrackController

- CuesInterface

- EMEController

- SubtitleStreamController

- SubtitleTrackController

- TimelineController

- CmcdController

Linter (ESlint)

Run linter:

Run linter with auto-fix mode:

Run linter with errors only (no warnings)

Formatting Code

Run prettier to format code

Run type-check to verify TypeScript types

Automated tests (Mocha/Karma)

Run all tests at once:

Run unit tests:

Run unit tests in watch mode:

Run functional (integration) tests:

An overview of this project's design, it's modules, events, and error handling can be found here .

API docs and usage guide

- API and usage docs, with code examples

- Auto-Generated API Docs (Latest Release)

- Auto-Generated API Docs (Development Branch)

Note you can access the docs for a particular version using " https://github.com/video-dev/hls.js/tree/deployments "

Latest Release

https://hlsjs.video-dev.org/demo

https://hlsjs-dev.video-dev.org/demo

Specific Version

Find the commit on https://github.com/video-dev/hls.js/tree/deployments .

Compatibility

HLS.js is only compatible with browsers supporting MediaSource extensions (MSE) API with 'video/MP4' mime-type inputs.

HLS.js is supported on:

- Chrome 39+ for Android

- Chrome 39+ for Desktop

- Firefox 41+ for Android

- Firefox 42+ for Desktop

- Edge for Windows 10+

- Safari 9+ for macOS 10.11+

- Safari for iPadOS 13+

- Safari for iOS 17.1+ since HLS version 1.5.0 using Managed Media Source (MMS) WebKit blog

A Promise polyfill is required in browsers missing native promise support.

Please note:

Safari browsers (iOS, iPadOS, and macOS) have built-in HLS support through the plain video "tag" source URL. See the example below (Using HLS.js) to run appropriate feature detection and choose between using HLS.js or natively built-in HLS support.

When a platform has neither MediaSource nor native HLS support, the browser cannot play HLS.

Keep in mind that if the intention is to support HLS on multiple platforms, beyond those compatible with HLS.js, the HLS streams need to strictly follow the specifications of RFC8216, especially if apps, smart TVs, and set-top boxes are to be supported.

Find a support matrix of the MediaSource API here: https://developer.mozilla.org/en-US/docs/Web/API/MediaSource

Using HLS.js

Installation.

Prepackaged builds are included with each release . Or install the hls.js as a dependency of your project:

A canary channel is also available if you prefer to work off the development branch (master):

Embedding HLS.js

Directly include dist/hls.js or dist/hls.min.js in a script tag on the page. This setup prioritizes HLS.js MSE playback over native browser support for HLS playback in HTMLMediaElements:

Alternative setup

To check for native browser support first and then fallback to HLS.js, swap these conditionals. See this comment to understand some of the tradeoffs.

For more embed and API examples see docs/API.md .

All HLS resources must be delivered with CORS headers permitting GET requests.

Video Control

Video is controlled through HTML <video> element HTMLVideoElement methods, events and optional UI controls ( <video controls> ).

Build a Custom UI

- Media Chrome

Player Integration

The following players integrate HLS.js for HLS playback:

- Akamai Adaptive Media Player (AMP)

- BridTV Player

- Flowplayer through flowplayer-hlsjs

- MediaElement.js

- KalturaPlayer through kaltura-player-js

- Videojs through Videojs-hlsjs

- Videojs through videojs-hls.js . hls.js is integrated as a SourceHandler -- new feature in Video.js 5.

- Videojs through videojs-contrib-hls.js . Production ready plug-in with full fallback compatibility built-in.

- Fluid Player

- OpenPlayerJS , as part of the OpenPlayer project

- CDNBye , a p2p engine for hls.js powered by WebRTC Datachannel.

They use HLS.js in production!

Chrome/firefox integration.

made by gramk , plays hls from address bar and m3u8 links

- Chrome native-hls

- Firefox native-hls

HLS.js is released under Apache 2.0 License

Code of conduct

Releases 285, used by 25.5k.

Contributors 278

- TypeScript 88.8%

- JavaScript 10.6%

Vivado HLS和Vitis HLS什么区别?

Vivado HLS 2020.1将是Vivado HLS的最后一个版本,取而代之的是VitisHLS。那么两者之间有什么区别呢?

Default User Control Settings

在Vitis HLS下,一个Solution的Flow Target可以是Vivado IP Flow Target,也可以是VitisKernel Flow Target,如下图所示。前者最终导出来的是VivadoIP,用于支持Vivado IP 设计流程。后者用于Vitis应用加速流程,此时,Vitis HLS会自动推断接口,无需在代码里通过Pragma或Directive的方式定义Interface,最终会输出.xo文件。

User Control Settings还有其他的一些变化,如下表所示。例如,在Vivado HLS下,默认是不会对循环设置Pipeline的,但在Vitis HLS下,只要循环边界小于64,就会对循环设置Pipeline。在Vivado HLS下,默认Clock Uncertainty是时钟周期的12.5%,但在Vitis HLS下更严格,达到了27%。

对循环而言,在Vivado HLS下,II(Initial Interval)默认的约束值为1,但在Vitis HLS下,II默认值为auto,意味着工具会尽可能达到最好的II。

目前,针对Vitis HLS,Xilinx已经提供了如下文档和设计案例:

UG1391:Vitis HLSMigration Guide

UG1399:VitisHigh-Level Synthesis User Guide

Vitis HLS examples: https://github.com/Xilinx/HLS-Tiny-Tutorials

本文分享自 Lauren的FPGA 微信公众号, 前往查看

如有侵权,请联系 [email protected] 删除。

本文参与 腾讯云自媒体分享计划 ,欢迎热爱写作的你一起参与!

Copyright © 2013 - 2024 Tencent Cloud. All Rights Reserved. 腾讯云 版权所有

深圳市腾讯计算机系统有限公司 ICP备案/许可证号: 粤B2-20090059 深公网安备号 44030502008569

腾讯云计算(北京)有限责任公司 京ICP证150476号 | 京ICP备11018762号 | 京公网安备号11010802020287

Copyright © 2013 - 2024 Tencent Cloud.

All Rights Reserved. 腾讯云 版权所有

HLSL Visiting Scholar & Researcher Library Services

Introduction, services & research tools, hollis - harvard's library catalog, legal & academic research databases, research guides, getting help, welcome to the harvard law school library.

This guide will introduce you to the resources and services available to visiting scholars and researchers at the Harvard Law School Library.

If you are interested in learning more about the process of applying to the Visiting Researcher and Visiting Scholar program, please consult the Harvard Law School's Graduate Program's Visiting Scholar and Researcher (VS/VR) webpage.

- Harvard Law School Visiting Scholar/Visiting Researcher Program

Visiting the Harvard Law School Library

Visit our website for details on access to the Harvard Law School Library. For any questions, contact our Access Services department.

- Harvard Law School Library: Use the Library Includes full library hours, and access and borrowing information.

Navigating the Library & the Law School

- Harvard Law School Library Spaces & Technology

- Finding Items at HLSL by Mindy Kent Last Updated Apr 18, 2024 81 views this year

- Campus Map & Directions

Research Services

- Harvard Law School Library Research Services Research Librarians are here to help you access our materials and develop strategies and skills to support your research

- Ask a Law Librarian Search our knowledge base, submit a question or request a one-on-one research consultation with a reference librarian to discuss specific areas of research or paper topics

- Request a Research Appointment Use this form to request a one-on-one meeting with a research librarian to help you effectively use our collections

Other Harvard Libraries

- Library.Harvard Explore the collections and services of the Harvard Library system

Computers & Printing

- Harvard Law School ITS Visit Harvard Law School Information Technology Services in the basement of Wasserstein for help with wifi and guest printing accounts.

- Printers, Scanners & Other Equipment in HLSL Locations of printers, scanners and photocopiers in the Harvard Law School Library

Research Tools

Harvard provides a number of useful tools that can be helpful as you start your research.

- Research Management and Citation Tools at Harvard Electronic citation tools can be a helpful way to organize resources and create bibliographies. This guide provides a comparison of some of the most commonly used citation tools

- Find a Journal Locate print or online journals at Harvard. Find articles online by title or citation.

- Harvard Lean Library Browser extension that provides quick and simple access to digital content purchased by Harvard Library.

What is HOLLIS?

HOLLIS, Harvard's library catalog includes records for millions of articles, books, journals, manuscripts, government documents, maps, microforms, music scores, sound recordings, visual materials, and data files.

- Search HOLLIS

Lexis, Westlaw & BloombergLaw

Visiting researchers are not automatically given passwords to Lexis, Westlaw & BloombergLaw, but exceptions can sometimes be made. Please contact the vendor representatives listed on the linked page to request passwords.

We also offer on-site access to Westlaw and Bloomberg terminals. You can also access legal content via NexisUni with your Harvard Key.

- Lexis, Westlaw & Bloomberg Law

- Westlaw & Bloomberg Terminals

- Nexis Uni Access via HarvardKey. Nexis Uni gives you access over 15,000 news, business, and legal sources. This source contains legal sources for federal and state cases and statutes, including U.S. Supreme Court decisions, print and online journals, business information on U.S. and international companies, national and regional newspapers, wire services, transcripts, international news, and non-English language sources. Use the included Company Dossier module to retrieve detailed company information and financial performance measures or identify and compare companies matching specific criteria. This product also provides access to Shepard’s Citations service for all federal and states court cases.

Other Legal Research Databases

The Library subscribes to a number of databases on topics related to the law and other related fields. Most are available onsite. Offsite access usually requires a Harvard Key log in.

- Legal Databases

Additional Harvard Databases

Researchers interested in searching across all of Harvard University's e-resources can search a more thorough list of databases across a full range of academic disciplines. Most will be available for use onsite or offsite with a current Harvard Key.

- Find a Database or E-Resource Find databases and e-resources at Harvard

Research Guides & Videos

The Library maintains research guides on a wide range of legal topicsThese guides give research tips related to particular areas of the law and also provide links and citation information for a range of resources on each topic.

- Harvard Law School Library Research Guides Searchable homepage for law guides, FAQs

- Research Guides & Videos Links to selected research guides, online study aids and library-created instructional videos

Research Guides on Other Topics

- Baker Library (HBS) Research Guides

- Kennedy School of Government Research Guides

- All Harvard Research Guides

Contact Us!

Ask Us! Submit a question or search our knowledge base.

Chat with us! Chat with a librarian (HLS only)

Email: [email protected]

Contact Historical & Special Collections at [email protected]

Meet with Us Schedule an online consult with a Librarian

Hours Library Hours

Classes View Training Calendar or Request an Insta-Class

Text Ask a Librarian, 617-702-2728

Call Reference & Research Services, 617-495-4516

- Last Updated: Apr 12, 2024 4:50 PM

- URL: https://guides.library.harvard.edu/law/visiting_researchers

Harvard University Digital Accessibility Policy

Application Toolkit: Written Statements

On this webpage, you will find our advice and guidance for approaching the two written statements in the application.

Beginning with the application for Fall Term 2024 enrollment, we now require that all applicants submit a Statement of Purpose and a Statement of Perspective. Although it is no longer an application component, much of the advice we shared about the personal statement may still be useful to applicants as they develop their Written Statements. We have preserved that information on this toolkit for your reference.

Changes to the J.D. Application Components

Instructions

Every applicant must submit both a Statement of Purpose and a Statement of Perspective, responding to the prompts below. Each Statement must be one to two pages in length, using double-spacing, one-inch margins, and a font size that is comfortable to read (no smaller than 11 point). We expect every applicant to use at least one full page for each Statement.

Statement of Purpose : What motivates you to pursue law? How does attending law school align with your ambitions, goals, and vision for your future?

Statement of Perspective : The Admissions Committee makes every effort to understand who you are as an individual and potential Harvard Law School student and graduate. Please share how your experiences, background, and/or interests have shaped you and will shape your engagement in the HLS community and the legal profession.

Blog Advice

- Visit the Admissions Blog

- View All Written Statements Blog Posts

Changes to the J.D. Program Application Components

August is here, and that means the J.D. Admissions Office is finalizing our application for the 2023–2024 cycle before it opens on September 15. One exciting change for this year: we have reworked our essay requirements and prompts.

August 4, 2023

Should you include a “why Harvard” statement in your application?

Each year at this time, we receive questions about how applicants should express interest in Harvard Law School. Include a “Why Harvard” essay? Talk about HLS in the personal statement? Maybe an addendum on this topic? The answer to all these questions is the same: no, that’s not necessary. Let’s start with the separate “why

December 2, 2022

Overrated/Underrated Part 3

Continuing our Overrated/Underrated series, this week, we shift our focus to highlight some of the overrated approaches that we recommend applicants avoid as they craft their applications.

November 17, 2021

Overrated/Underrated Part 1

The J.D. Admissions team recently came together to offer their thoughts on some underrated and overrated approaches that applicants might take towards their HLS application. We hope you’ll find some of these nuggets useful.

September 9, 2021

Real Talk: The Personal Statement

For our first entry in the Real Talk series, Associate Director Nefyn Meissner shares advice on approaching the personal statement.

August 6, 2020

Personal Statement Advice

The personal statement is “an opportunity to give the Admissions Committee a better sense of who you are as a person and as a potential student and graduate of Harvard Law School.” But what does that mean to us?

November 6, 2018

Podcast Advice

Navigating law school admissions with miriam & kristi.

Miriam Ingber (Associate Dean of Admissions and Financial Aid at Yale Law School) and Kristi Jobson (Assistant Dean for Admissions at Harvard Law School) provide candid, accurate, and straightforward advice about law school admissions — direct from the source. They will be joined by guest stars from other law schools to discuss application timing, letters of recommendation, personal statements, and more.

- View All Episodes

Written Statements Workshop

Our Statement Workshop provides applicants with straightforward advice on how to craft essays with a reflective activity and guiding questions to consider.

We do understand mistakes happen. You are more than welcome to upload an updated document through your status checker. We will review the new material alongside what has been previously received.

Note that when you complete your application and hit “submit”, the information contained in your application may not be altered or deleted in any way by you as an applicant or by us as an admissions team.

Yes. Reapplicants will need to submit new written statements with their application.

We ask that transfer candidates also address the reason(s) for applying for transfer enrollment. Please visit our Transfer Applications Components for more information.

Modal Gallery

Gallery block modal gallery.

IMAGES

VIDEO

COMMENTS

Visit Planning Tools. Trains and Bus Information: Massachusetts Bay Transportation Authority (MBTA) Taxi Information: Cambridge Taxi Cab: 1-617-649-7000 | Ambassador Brattle Cab: 1-617-547-3000. Parking Information: Visitor Parking at Harvard Law School. Nearby Attractions: Boston Visitors Guide.

Harvard Law School provides unparalleled opportunities to study law with extraordinary colleagues in a rigorous, vibrant, and collaborative environment.

Harvard Law School is the oldest continuously operating law school in the United States and is home to the largest academic law library in the world. Visit HLS: Campus Map and Directions. Harvard Law School combines genuine excellence and wonderful diversity on a scale that is unmatched anywhere. No law school has done more to shape law or ...

Vitis™ HLS 工具允许用户通过将 C/C++ 函数综合至 RTL 中来轻松创建复杂的 FPGA 算法。Vitis HLS 工具与面向综合和布局布线的 Vivado™ Design Suite 以及面向异构系统设计和应用的 Vitis™ 统一软件平台紧密集成。

The Vitis™ HLS tool allows users to easily create complex FPGA algorithms by synthesizing a C/C++ function into RTL. The Vitis HLS tool is tightly integrated with both the Vivado™ Design Suite for synthesis and place & route and the Vitis™ unified software platform for heterogenous system designs and applications.

Vitis HLS 工具与 Vivado™ Design Suite(用于综合、布置和布线)及 Vitis™ 统一软件平台(用于所有异构系统设计和应用)高度集成。 使用 Vitis HLS 流程,用户可针对 C 代码应用指令,创建专门用于所需实现方案的 RTL。

Vitis HLS. The Vitis HLS tool allows users to easily create complex FPGA algorithms by synthesizing a C/C++ function into RTL. The Vitis HLS tool is tightly integrated with both Vivado™ ML Design Suite for synthesis and place & route and the Vitis unified software platform for heterogenous system designs and applications.

There will be no automatic loop pipelining unless "config_compile -pipeline_loops" is set. For such cases, "#pragma HLS pipeline off" can be used to disable pipelining for certain loops. Note that this only applies to Vitis HLS (and not Vivado HLS). Please refer to the documentation below:

Xilinx Vitis HLS 2020.1 beta 初体验(一). 盛碗粥. 防秒退提醒:本文比较了基于现有 Vivado HLS 2019.2 和最新版本的 Vitis HLS 2020.1 的硬件设计步骤来看 Xilinx 在 HLS 上最近的进展。. 本文(一)初步测试了新版 Vitis HLS 中声称的自动优化代码的功能。. 0. 背景. 在今年的 ...

HLS has 4 departments that make up the school: Central Eurasian Studies, East Asian Languages and Cultures, International Studies, and Middle Eastern Languages and Cultures. There are more than 21 area studies institutes and centers in the school, so you can study practically any region of the globe you desire.

Usually I only used Vitis HLS IDE to generate the custom IP core. After that, I will used vivado IDE to connect my custom IP with the embedded processor in the board and generate the bit stream. For developing the software for host processor, I usually used PYNQ framework (This is the github source in which I learn my current workflow: https ...

The Houston Livestock Show and Rodeo™ promotes agriculture by hosting an annual, family-friendly experience that educates and entertains the public, supports Texas youth, showcases Western heritage and provides year-round educational support within the community. ABOUT US.

A Tcl file is provided: run_hls.tcl: Sets up the project and specifies what steps of the flow will be executed (by default only C simulation and C synthesis are run). To run at the command line, navigate to the example directory, type: vitis_hls -f run_hls.tcl. To load the design into the HLS GUI, "Open"->"Project file" and select the project ...

The Human Landing System (HLS) is the mode of transportation that will take astronauts to the lunar surface as part of the Artemis program, including the first woman and the first person of color. The program is managed at Marshall Space Flight Center in Huntsville, Alabama. Crews will board the HLS in lunar orbit and descend to the surface ...

After three seasons, Miriam Ingber and Kristi Jobson, the deans of admission at Yale Law School and Harvard Law School, are taking their podcast, Navigating Law School Admissions, on the road. They've partnered with law firms to host live events in Boston, New York City, Seattle, and Los Angeles this fall. Join them in a city near you as they ...

The Hamilton Lugar School wishes to acknowledge and honor the Miami, Delaware, Potawatomi, and Shawnee people, on whose ancestral homelands and resources Indiana University was built. The Hamilton Lugar School of Global and International Studies offers undergraduate and graduate programs in several areas of foreign relations, policy, and affairs.

Table of Contents. Xilinx Vitis HLS (formerly Xilinx Vivado HLS) is a High-Level Synthesis (HLS) tool developed by Xilinx and available at no cost. Vitis HLS allows the user to easily create complex FPGA-based algorithms using C/C++ code. It supports complex data types (floating-points, fixed-points,…) and math functions (sine, arctan, sqrt,…).

HLS Virtual Campus Tour Harvard Law School provides unmatched opportunities to study law and related disciplines in a rigorous and collaborative environment. Harvard's scope is measured in its unparalleled breadth and depth of courses and clinics, its wide array of research programs, its diverse student body drawn from across the nation and ...

When a platform has neither MediaSource nor native HLS support, the browser cannot play HLS. Keep in mind that if the intention is to support HLS on multiple platforms, beyond those compatible with HLS.js, the HLS streams need to strictly follow the specifications of RFC8216, especially if apps, smart TVs, and set-top boxes are to be supported.

User Control Settings还有其他的一些变化,如下表所示。. 例如,在Vivado HLS下,默认是不会对循环设置Pipeline的,但在Vitis HLS下,只要循环边界小于64,就会对循环设置Pipeline。. 在Vivado HLS下,默认Clock Uncertainty是时钟周期的12.5%,但在Vitis HLS下更严格,达到了27%。. 对 ...

TORONTO, April 25, 2024 /CNW/ - HLS Therapeutics Inc. ("HLS" or the "Company") (TSX: HLS), announces that it will release its Q1 fiscal 2024 financial results on Thursday, May 9, 2024.The Company will hold a conference call that same day at 8:30 a.m. ET to discuss its results. The call will be hosted by Mr. Craig Millian, Chief Executive Officer and Mr. John Hanna, Interim Chief Financial Officer.

This guide will introduce you to the resources and services available to visiting scholars and researchers at the Harvard Law School Library. If you are interested in learning more about the process of applying to the Visiting Researcher and Visiting Scholar program, please consult the Harvard Law School's Graduate Program's Visiting Scholar and Researcher (VS/VR) webpage.

The Calendar@Law e-mail also includes administrative notices about employment opportunities and other matters of interest. This e-mail provides a quick and easy way to stay abreast of law school events and activities. For a full calendar of HLS events, visit hls.harvard.edu/calendar. News@Law and Harvard Law Today

3.1 Vitis HLS工程建立. (1)新建Vitis HLS工程,如下图所示,工程名为"HLS_StartDemo";. (2)指定要综合的顶层函数名称,此处我们填写待综合的函数名称为"VectorAdd";. (3)可以在建立工程的时候,暂时不添加Testbench文件。. (4)创建Solution,同时要指定Solution ...

On this webpage, you will find our advice and guidance for approaching the two written statements in the application. Instructions Every applicant must submit both a Statement of Purpose and a Statement of Perspective, responding to the prompts below. Each Statement must be one to two pages in length, using double-spacing, one-inch margins, and a […]